# CS 151 Midterm

| Name       | · |             |              |  |

|------------|---|-------------|--------------|--|

|            |   | (Last Name) | (First Name) |  |

| Student ID | : |             |              |  |

| Signature  | : |             |              |  |

#### **Instructions:**

- 1. Please verify that your paper contains 11 pages including this cover.

- 2. Write down your Student-Id on the top of each page of this quiz.

- 3. This exam is **closed book**. No notes or other materials are permitted.

- 4. Total credits of this midterm are **70 points.**

- 5. To receive credit you must show your work clearly.

- 6. For possible re-grade request make sure that your write clearly.

- 7. Calculators are **NOT** allowed.

### Q1: [ALU] [20 points]

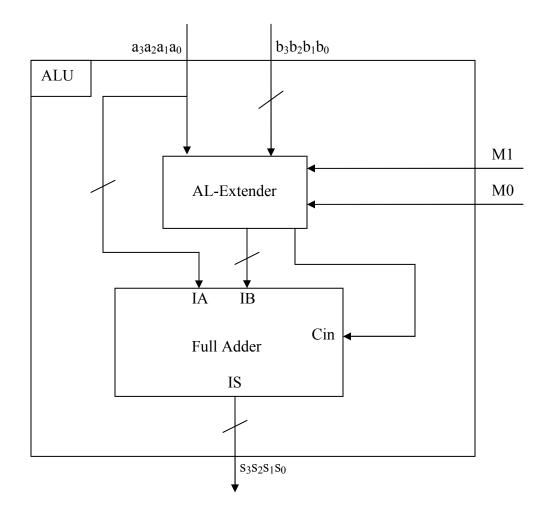

We are going to design a 4-bit Arithmetic Unit (AU) with the following functional table:

| M1 | M0 | Function Name                             | F(A,B)                  |

|----|----|-------------------------------------------|-------------------------|

| 0  | 0  | A + A multiplied by 8 times B             | A*(8*B)+A               |

| 0  | 1  | If (A>B) subtract B from A; otherwise add | If (A>B) then A-B; else |

|    |    | A and B                                   | A+B                     |

| 1  | 0  | Decrement A                               | A-1                     |

| 1  | 1  | Add 1 to A+B                              | A+B+1                   |

A and B are two 4-bit binary numbers <u>a3a2a1a0</u> and <u>b3b2b1b0</u>.

M1, M0 are the control inputs to this AU.

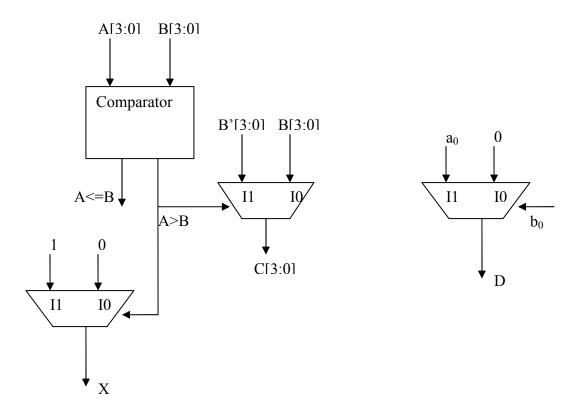

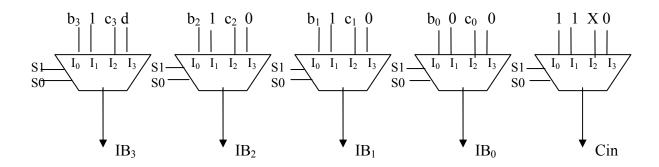

For doing this, the block labeled "AL-Extender" in the following block diagram should be designed.

In this question you should design the logic inside AL-Extender using JUST <u>Comparators</u> and <u>Multiplexers</u> if needed.

| Student ID: |  |

|-------------|--|

|             |  |

#### **Q2:** [High-Level State Machine Design]

[15 points]

Design the high-level state machine for a DVD player with the following functionality: Initially when we turn on the system it is in **STOP** mode and we can assume that there is a DVD already inserted in. The DVD player has four buttons: STOP, PLAY, FF (Fast Forward) and FB (Fast Backward). While in STOP mode if we hit STOP or FF or FB button we should stay at the same state. As well whenever we reach the STOP mode the value of the timer resets to **ZERO**. Once we hit PLAY button, the DVD player starts playing and every cycle the timer of the player is incremented by one unless it reaches the end of the DVD (time 200) when it goes to STOP mode automatically. While in play mode if we hit FF button and keep it depressed for just one clock cycle the timer is incremented by 50 and then we automatically go back to play mode. If we hit the FF button the next clock cycle the DVD player goes to Fast Forward mode and the timer is incremented by 5 for each cycle. The DVD player will remain at the same state unless: we hit the PLAY button or the FB button which takes us to the PLAY mode; or the end of the DVD is reached or we hit the STOP button which puts the player in STOP mode; The same thing happens if we push FB button with the difference that the timer is decremented by the same amount of FF mode. The player remains at FB mode unless: we hit the PLAY button or the FF button which takes the player to the PLAY mode; the beginning of the DVD is reached where the timer is set to ZERO and the player goes to the PLAY mode automatically; the STOP button is hit which puts the player in STOP mode:

| Student ID: |  |

|-------------|--|

|             |  |

# Q3: [RTL design]

[35 points]

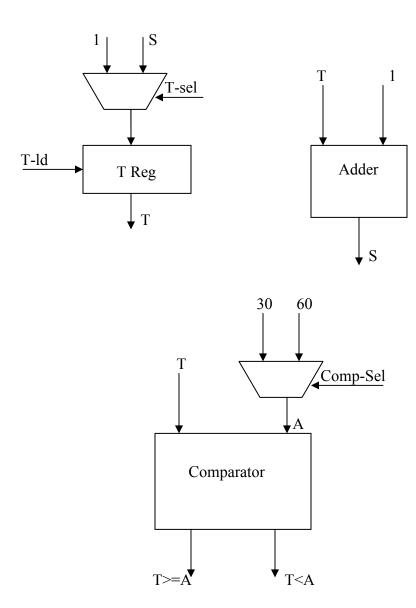

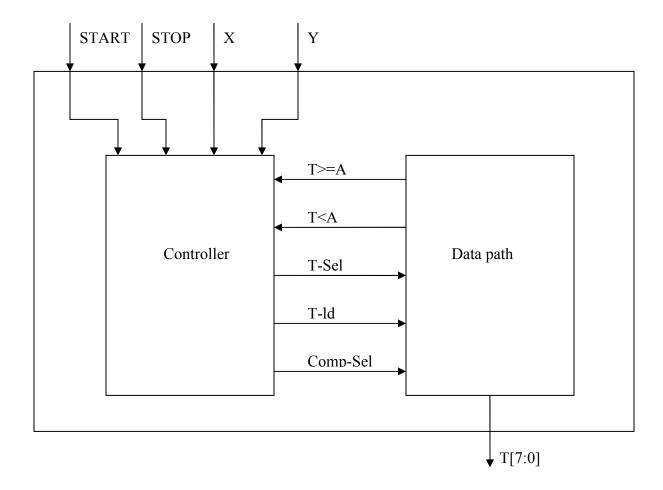

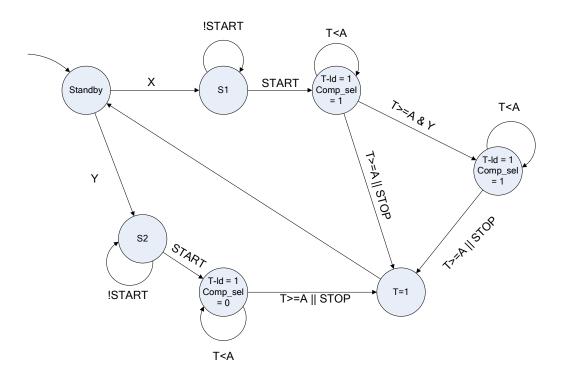

Considering the following high-level state machine and assuming that X, Y, START and STOP are one bit control inputs and T is an 8-bit output of the circuit:

# 3a. Design the data-path for this system. [15 points]

# 3b. Design the interface of the system and the interface between the controller and the datapath. [5 points]

#### 3c. Design the FSM of the controller. [15 points]

HINT: There is no timing issue for this system so you do not have to consider timing issues in designing the controller's FSM.

In fact there is a timing issue in each of the states that increments T. To solve the timing issue we have to add a "dummy" state for each problematic state. This "dummy" state is just supposed to provide one more clock cycle for the register to load the value. All the incoming edges still enter to the original state. On the other hand all the outgoing edges exit the "dummy" state.

For the sake of grading, the students do not have to be concerned about the timing issue as the problem had wanted them to ignore it.

| Student ID: |  |

|-------------|--|

|             |  |